導入事例

2014/05/08

[導入事例] 国立情報学研究所 定兼先生

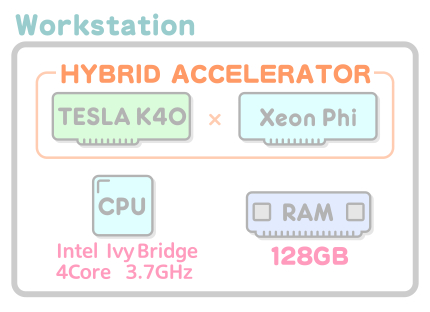

GPGPU & Xeon Phi 同時搭載のハイブリッドアクセラレータ搭載高速計算機を導入頂きました。

研究内容

研究内容の紹介

・大量データ処理のためのアルゴリズムとデータ構造。

・圧縮したままデータを処理できる圧縮方法、簡潔データ構造の理論と応用。

・GPUなどのメニーコア環境での計算モデルとアルゴリズムの開発。

研究室の紹介

国立情報学研究所 ホームペ-ジ

東京大学 ホームペ-ジ

http://www.keisu.t.u-tokyo.ac.jp/lab/lab_mist/member/lab_07_2.html

東京大学 定兼先生のホームペ-ジ

プロフィール

2000年 東京大学大学院理学系研究科情報科学専攻修了。博士(理学)。

2000年 東北大学大学院情報科学研究科助手。

2003年 九州大学大学院システム情報科学研究院助教授(准教授)。

2009年 国立情報学研究所准教授。

2014年 同教授

2014年 東京大学大学院情報理工学系研究科教授。

受賞

2009年10月 モバイル・コミュニケーション・ファンド ドコモ・モバイル・サイエンス賞

2007年11月 日本IBM科学賞

2007年4月 文部科学大臣表彰 若手科学者賞

2006年4月 船井情報科学振興財団 船井情報科学奨励賞

2002年9月 情報処理学会 山下記念研究賞

1998年3月 IEEE Data Compression Conference Copocelli Prize

1998年3月 電子情報通信学会データ工学専門委員会 データ工学ワークショップ奨励賞

論文及び研究業績

以下を参照願います。

導入システム

導入システムと使おうと思ったきっかけ、用途・狙い・目的など

毎年行われているHPCSの展示コーナーでHPCテック製品の紹介を受けました。CPU、GPUを使ったメニーコア環境での計算モデルとアルゴリズムの開発を行っています。現在はGPU用の計算モデルとアルゴリズムの開発を行っており、最新のアーキテクチャでのアルゴリズムの評価を行うためにTesla K40を導入しました。また、GPUではアルゴリズムに制約が入るために開発が難しくなるため、より自由度の高いIntel Xeon Phiも導入しました。

これまでの計算機と比べた感想を教えて下さい

これまでTesla K20を使った開発を行ってきましたが、K40の12 GBというオンボードメモリや新世代のPCI Express Generation 3.0で二倍に拡張したバス幅を生かした高速アルゴリズムを開発しようと思っています。またGPUとIntel Xeon Phiのように異なるアーキテクチャの混在する環境のための計算モデルの開発も行う予定です。

今後の展望

最新のハードウェア環境はまだ十分に活用しきれていません。今回は1ノードの中にTesla K40とIntel Xeon Phiを同時に運用して来ましたが、今後1ノードの中に複数枚のTeslaやIntel Xeon Phiを同時に搭載させたり、Tesla やIntel Xeon Phiを同時に搭載させたノードを複数ノードに増やした環境でのアルゴリズム開発にチャレンジしたいと思います。