HPCTECH Solution

- トップページ

- 製品案内:ハードウェア

- 開発コード名:Genoa, Genoa-X, Bergamo

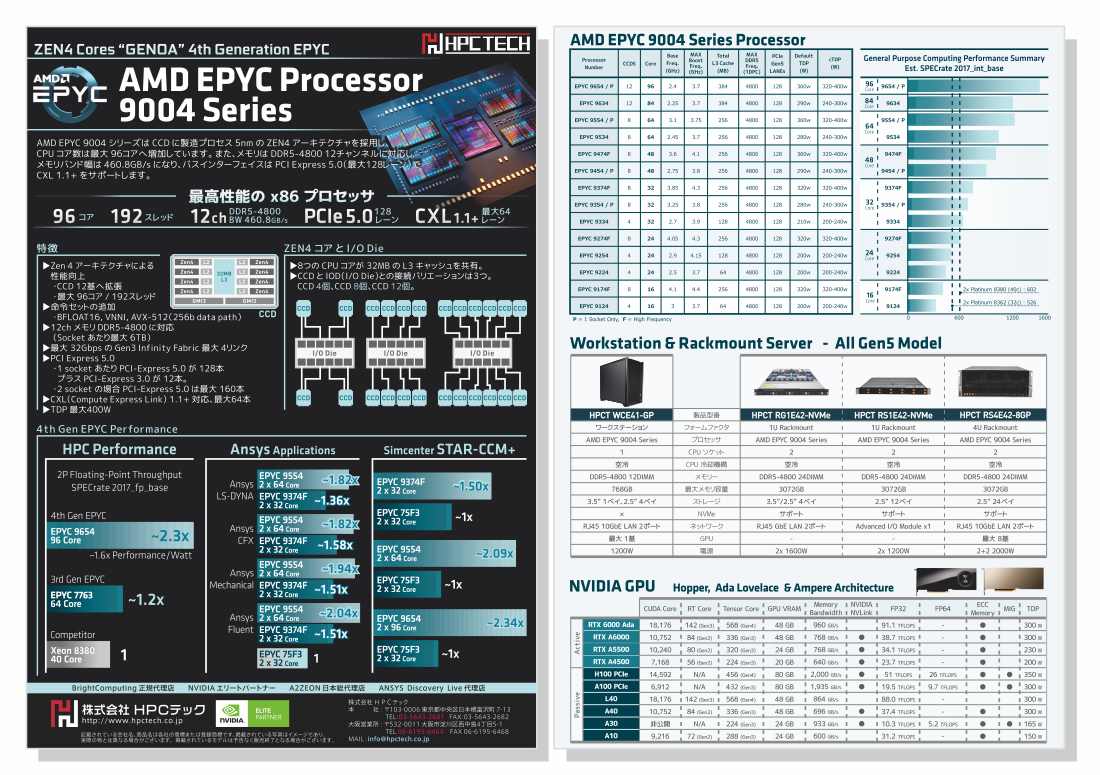

AMD EPYC 9004 Series

AMD EPYC プロセッサ 9004 シリーズ特徴

・開発コード名:Genoa

・Zen3 から Zen 4 アーキテクチャへ。

製造プロセス 5nm

・CCD は12基へ拡張。

96 コア / 192 スレッドへ増加。

・命令セットの追加。

BFLOAT16, VNNI, AVX-512(256b data path)

・12ch メモリ DDR5-4800 に対応。

(Socket あたり最大 6TB)

・最大 32Gbps の Gen3 Infinity Fabric 最大 4リンク。

・PCI Express 4.0 から PCI Express 5.0へ。

1 socket あたり PCI-Express 5.0 が 128本 + PCI-Express 3.0 12本。

2 socket の場合 PCI-Express 5.0 は最大 160本。

・CXL 1.1+ 最大64本

・専用セキュリティサブシステム等を強化

・TDP 最大400W

・開発コード名:Genoa-X

・3D V-Cache搭載。

・最大 1.1TB の L3キャッシュ

・開発コード名:Bergamo

・Zen 4c アーキテクチャ採用。

・CCD は 8基。

最大 128 コア / 256 スレッド。

・AVX-512 の完全サポート

(BFLOAT16 と VNNI 命令など含む)

・12ch メモリ DDR5-4800 に対応。

・PCI Express 5.0

・TDP 最大360W

AMD EPYC プロセッサ 9004 シリーズ仕様

| Processor Number |

Cores | Threads | Base Freq. (GHz) |

MAX Boost Freq. (GHz) |

Total L3 Cache (MB) |

DDR5 Channels |

MAX DDR5 Freq. (1DPC) |

PCIe Gen5 LANEs |

Default TDP (W) |

| EPYC 9754 | 128 | 256 | 2.25 | 3.10 | 256 | 12 | 4800 | 128 | 360 |

| EPYC 9754S | 128 | ||||||||

| EPYC 9734 | 112 | 224 | 2.20 | 3.00 | 256 | 12 | 4800 | 128 | 340 |

| EPYC 9654 / P | 96 | 192 | 2.40 | 3.70 | 384 | 12 | 4800 | 128 | 360 |

| EPYC 9634 | 84 | 168 | 2.25 | 3.70 | 384 | 12 | 4800 | 128 | 290 |

| EPYC 9554 / P | 64 | 128 | 3.10 | 3.75 | 256 | 12 | 4800 | 128 | 360 |

| EPYC 9534 | 64 | 128 | 2.45 | 3.70 | 256 | 12 | 4800 | 128 | 280 |

| EPYC 9454 / P | 48 | 64 | 2.75 | 3.80 | 256 | 12 | 4800 | 128 | 290 |

| EPYC 9354 / P | 32 | 64 | 3.25 | 3.80 | 256 | 12 | 4800 | 128 | 280 |

| EPYC 9334 | 32 | 56 | 2.70 | 3.90 | 128 | 12 | 4800 | 128 | 210 |

| EPYC 9254 | 24 | 48 | 2.90 | 4.15 | 128 | 12 | 4800 | 128 | 200 |

| EPYC 9224 | 24 | 48 | 2.50 | 3.70 | 64 | 12 | 4800 | 128 | 200 |

| EPYC 9124 | 16 | 32 | 3.00 | 3.70 | 64 | 12 | 4800 | 128 | 200 |

| WITH AMD 3D V-CACHE | |||||||||

| EPYC 9684X | 96 | 192 | 2.55 | 3.70 | 1152 | 12 | 4800 | 128 | 400 |

| EPYC 9384X | 32 | 64 | 3.10 | 3.90 | 768 | 12 | 4800 | 128 | 320 |

| EPYC 9184X | 16 | 32 | 3.55 | 4.20 | 768 | 12 | 4800 | 128 | 320 |

| HIGH - FREQUENCY MODEL | |||||||||

| EPYC 9474F | 48 | 96 | 3.60 | 4.10 | 256 | 12 | 4800 | 128 | 360 |

| EPYC 9374F | 32 | 64 | 3.85 | 4.30 | 256 | 12 | 4800 | 128 | 320 |

| EPYC 9274F | 24 | 48 | 4.05 | 4.30 | 256 | 12 | 4800 | 128 | 320 |

| EPYC 9174F | 16 | 32 | 4.10 | 4.40 | 256 | 12 | 4800 | 128 | 320 |

CPU CORE INNOVATION - 初代 EPYC ~ 第4世代 EPYC スペック比較

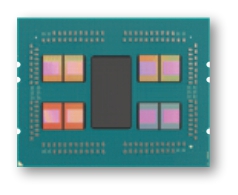

AMD EPYC プロセッサは、「CPU コア」と 「I/O 機能」 2つのイノベーションパスを 2つの異なるタイプのダイに分離し、必要なことに適したタイムラインで開発できるようにしました。最新の第 4世代プロセッサでは、Zen 4 CPU ダイは 5nm テクノロジで製造され、I/O DIE は 6nm プロセスで製造されています。 AMD EPYC 9004 シリーズ プロセッサは、最大 8個のコアと大規模な L3 キャッシュを持つ、最大 12個の CPU DIE と I/O ダイで構築されています。前世代と比較して 1ワットあたりの整数が推定 24% 向上し、浮動小数点トップオブスタックのパフォーマンスが 52% 向上しました。

| AMD EPYC 7001 NAPLES |

AMD EPYC 7002 ROME |

AMD EPYC 7003 MILAN |

AMD EPYC 9004 GENOA GENOA-X BERGAMO |

|

|

|

|

|

|

| Core Architecture | Zen | Zen 2 | Zen 3 | Zen 4, Zen 4c |

| Cores | 8 to 32 | 8 to 64 | 8 to 64 | 16 to 128 |

| Max L3 Cache |

Up to 64 MB | Up to 256 MB | Up to 256 MB* | Up to 384 MB |

| Max L3 Cache with 3D V-Cache technology | - | - | 768 MB | Up to 1152 MB |

| PCIe Lanes |

Up to 128 Gen 3 | Up to 128 Gen 3 | Up to 128 Gen 4 | Up to 128 Gen 5 8 bonus lanes Gen 3 |

| CPU Process Technology |

14 nm | 7 nm | 7 nm | 5 nm |

| I/O Die Process Technology |

N/A | 14 nm | 14 nm | 6 nm |

| cTDP | 120-200W | 120-280W | 155-280W | 200-400W |

| Max Memory Capacity | 2 TB DDR3-2400/2666 |

4 TB DDR4-3200 |

4 TB DDR4-3200 |

6 TB DDR5-4800 |

Core Complex (CCX) and Core Complex Die (CCD)

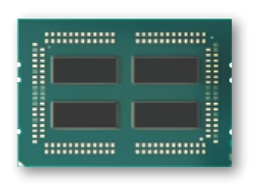

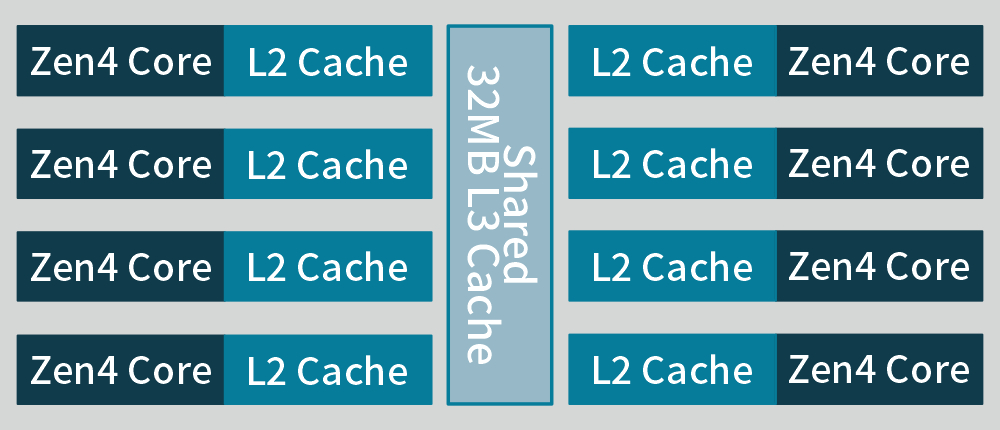

Genoa CCD - Zen4

8コアで 32MB L3キャッシュを共有

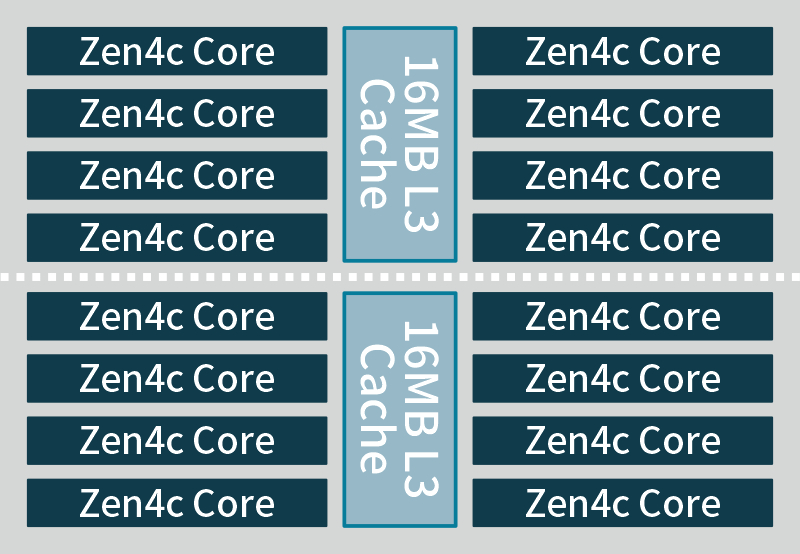

Bergamo CCD - Zen4c

8コアで 16MB L3キャッシュを共有

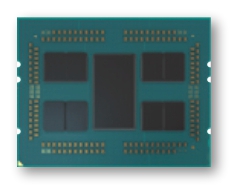

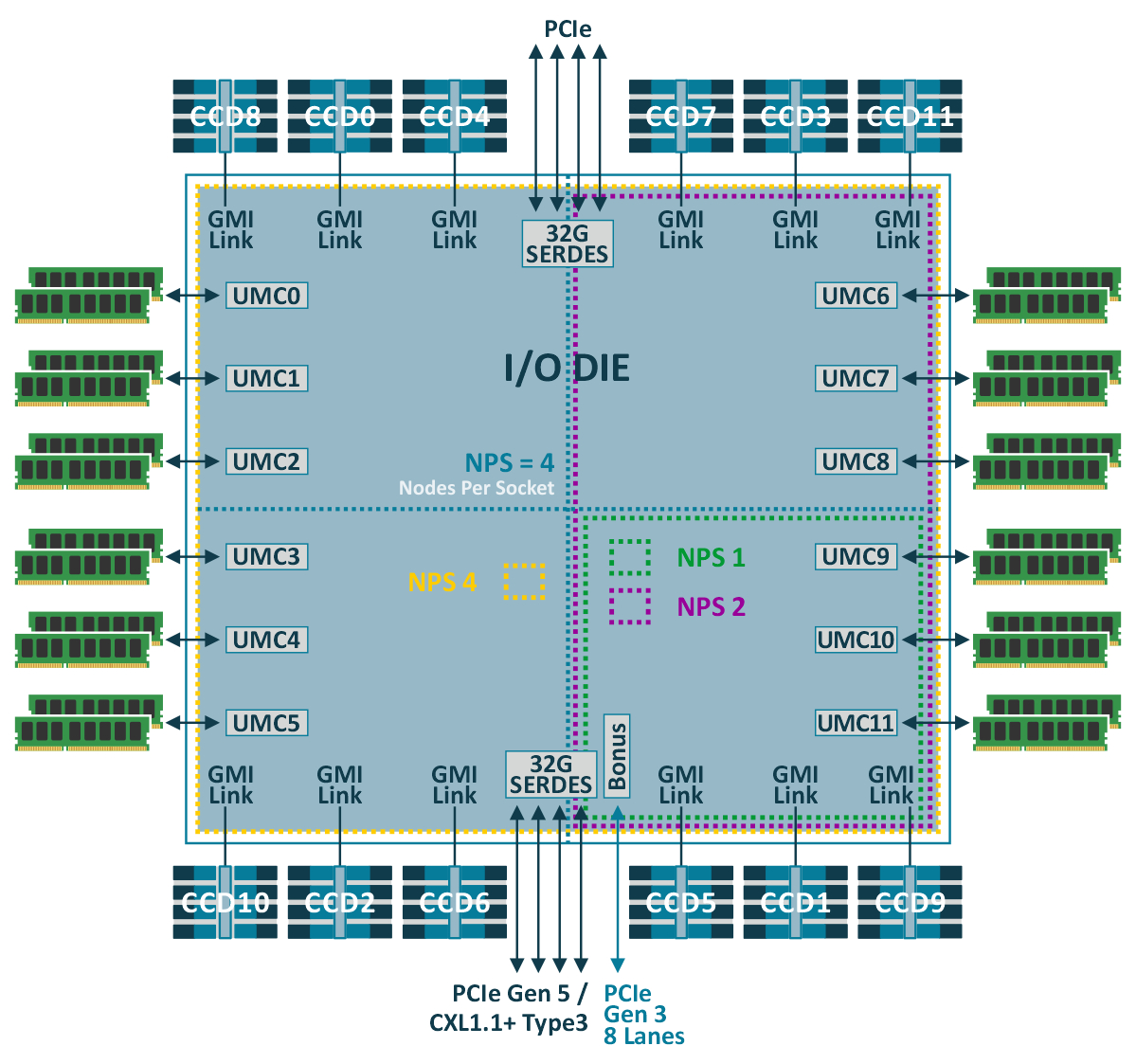

I/O DIE

AMD EPYC 9004 シリーズプロセッサには、SoC(systems on chip)ごとに最大 12個の CCD をサポートする最新の I/O ダイが含まれています。各 CCD は専用の高速グローバルメモリインターコネクト(GMI)リンクを介して I/O DIE に接続します。 I/O DIE は、DDR5 メモリチャネルや PCIe Gen5、CXL 1.1+、および Infinity Fabric リンクへと展開します。

AMD EPYC 9004 シリーズでは PCIe Gen5 機能を I/O DIE に組み込むことで、CPU の I/O 帯域幅を過去の世代の 2倍にしました。 I/O 帯域幅を 2倍にするだけではなく、I/O ダイ上の I/O サブシステムは、AMD Infinity Fabric インターコネクト、SATA ディスク コントローラー、Compute Express Link (CXL) 1.1+ メモリー コントローラーを柔軟にサポートします。

NUMA Topology

AMD EPYC 9004 シリーズプロセッサは、Non-Uniform Memory Access (NUMA) アーキテクチャを使用しており、ユーザはシステムの NUMA Nodes Per Socket (NPS) BIOS 設定を調整して特定の動作環境とワークロードに合わせてこの NUMA トポロジを最適化できます。

NPS=4

プロセッサはソケットごとに 4つの NUMA ノードに分割され、各論理象限が独自の NUMA ノードとして構成されます。メモリは各象限に関連付けられたメモリ チャネル全体にインターリーブされます。 PCIe デバイスはそのデバイスの PCIe ルートコンプレックスを持つ象限 (I/O ダイの) に応じて、4つの NUMA ノードのいずれかのローカルになります。

NPS=2

ソケットごとに 2つの NUMA ノードが構成されます。メモリは各半分に関連付けられたメモリ チャネル全体にインターリーブされます。 PCIe デバイスはそのデバイスの PCIe ルートコンプレックスを持つ象限 (I/O ダイの) に応じて、2つの NUMA ノードのいずれかのローカルになります。

NPS=1

ソケットごとに単一の NUMA ノードを示します。この設定によりプロセッサ上のすべてのメモリチャネルが 1つの NUMA ノードに構成されます。すべてのプロセッサコア、すべてのメモリ、および SoC に接続されているすべての PCIe デバイスは、その 1つの NUMA ノードに接続されています。メモリはプロセッサ上のすべてのメモリチャネルにわたって単一のアドレス空間にインターリーブされます。

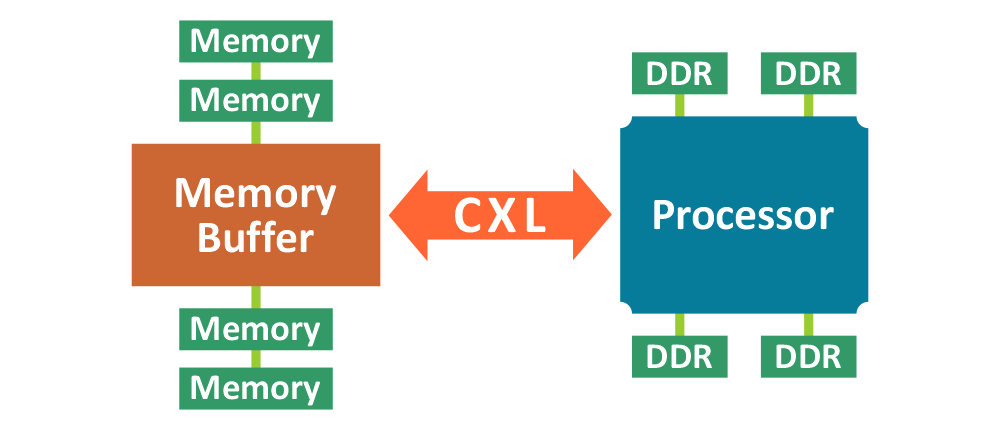

CXL 1.1+ Type 3

CXL Memory Module を搭載しメモリバッファとして使用することが出来ます。

Memory Buffers

Usages:

・Memory BW expansion

・Memory capacity expansion

・2LM

Protocols:

・CXL.io

・CXL.mem

性能比較 - 2P 4th Gen EPYC vs 2P 3rd Gen Xeon

Per-Core Integer Performance Leadership

4th Gen EPYC CPUs Outperform 3rd Gen Xeon Scalable Options

Estimated SPECrate 2017 Integer Throughput Performance Uplift

| 16-Core | EPYC 9174F | Up to 44% | ||

| Xeon Gold 6346 | ||||

| 32-Core | EPYC 9374F | Up to 45% | ||

| Xeon Platinum 8362 | ||||

| 48-Core | EPYC 9474F | Up to 44% | ||

| 40-Core | Xeon Platinum 8380 |

Per-Core Floating Point Performance Leadership

4th Gen EPYC CPUs Outperform 3rd Gen Xeon Scalable Options

Estimated SPECrate 2017 Floating-Point Throughput Performance Uplift

| 16-Core | EPYC 9174F | Up to 73% | ||

| Xeon Gold 6346 | ||||

| 32-Core | EPYC 9374F | Up to 81% | ||

| Xeon Platinum 8362 | ||||

| 48-Core | EPYC 9474F | Up to 78% | ||

| 40-Core | Xeon Platinum 8380 |

アプリケーション性能比較 - 2P 4th Gen EPYC 64Core vs 2P 3rd Gen EPYC 32Core

Ansys Applications

Ansys LS-DYNA - Up to ~1.72x uplift on

| 2 x 64 Cores | EPYC 9554 | ~1.82x | ||

| 2 x 32 Cores | EPYC 9374F | ~1.36x | ||

| 2 x 32 Cores | EPYC 75F3 |

Ansys CFX - Up to ~1.75x uplift on

| 2 x 64 Cores | EPYC 9554 | ~1.91x | ||

| 2 x 32 Cores | EPYC 9374F | ~1.58x | ||

| 2 x 32 Cores | EPYC 75F3 |

Ansys Mechanical - Up to ~1.84x uplift on

| 2 x 64 Cores | EPYC 9554 | ~1.94x | ||

| 2 x 32 Cores | EPYC 9374F | ~1.51x | ||

| 2 x 32 Cores | EPYC 75F3 |

Ansys Fluent - Up to ~2.08x uplift on

| 2 x 64 Cores | EPYC 9554 | ~2.04x | ||

| 2 x 32 Cores | EPYC 9374F | ~1.51x | ||

| 2 x 32 Cores | EPYC 75F3 |

Simcenter STAR-CCM+

Up to ~1.50x with 32-core - 4th Gen AMD EPYC CPUs

| 2 x 32 Cores | EPYC 9374F | ~1.50x | ||

| 2 x 32 Cores | EPYC 75F3 |

Up to ~2.09x with 64-core - 4th Gen AMD EPYC CPUs

| 2 x 64 Cores | EPYC 9554 | ~2.09x | ||

| 2 x 32 Cores | EPYC 75F3 |

Up to ~2.34x with 96-core - 4th Gen AMD EPYC CPUs

| 2 x 96 Cores | EPYC 9654 | ~2.34x | ||

| 2 x 32 Cores | EPYC 75F3 |

AMD EPYC テクニカル・ドキュメント&ホワイトペーパー

4TH GEN AMD EPYC PROCESSOR ARCHITECTURE

https://www.amd.com/system/files/documents/4th-gen-epyc-processor-architecture-white-paper.pdf

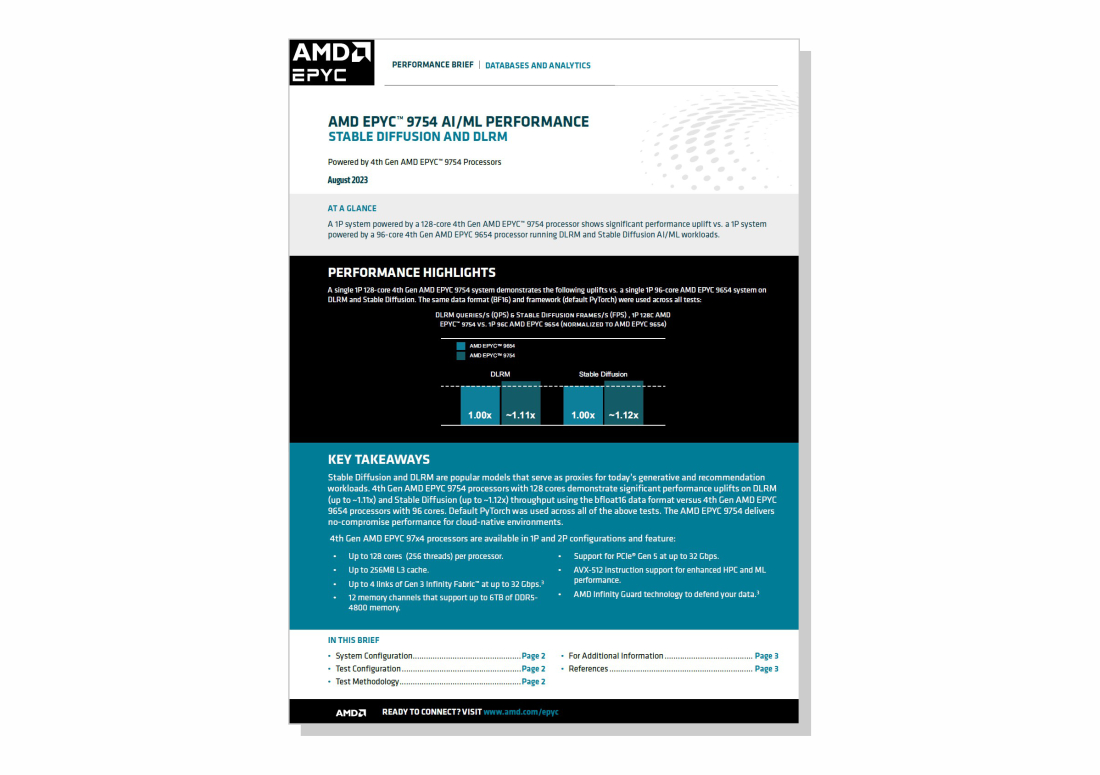

AMD EPYC 9754 AI/ML PERFORMANCE

STABLE DIFFUSION AND DLRM

Powered by 4th Gen AMD EPYC 9754 Processors

CLOUD-NATIVE WORKLOADS ON AMD EPYC 9754 PROCESSORS

COMPREHENSIVE PERFORMANCE LEADERSHIP

Powered by 4th Gen AMD EPYC 9754 Processors

AMD Documentation Hub

Spack support of HPC applications

Spack は複雑な科学ソフトウェアをインストールするためのパッケージ管理フレームワークとツールを提供するオープンソースプロジェクトです。Spack パッケージで AMD Optimized CPU Compilers and Libraries (AOCC および AOCL ) をサポートしており、多くの異なるプラットフォームや環境でソフトウェア複数のバージョンと構成をサポートするように設計されています。

https://developer.amd.com/spack/

AMD EPYC 9004 シリーズカタログ